Metodo di pagamento

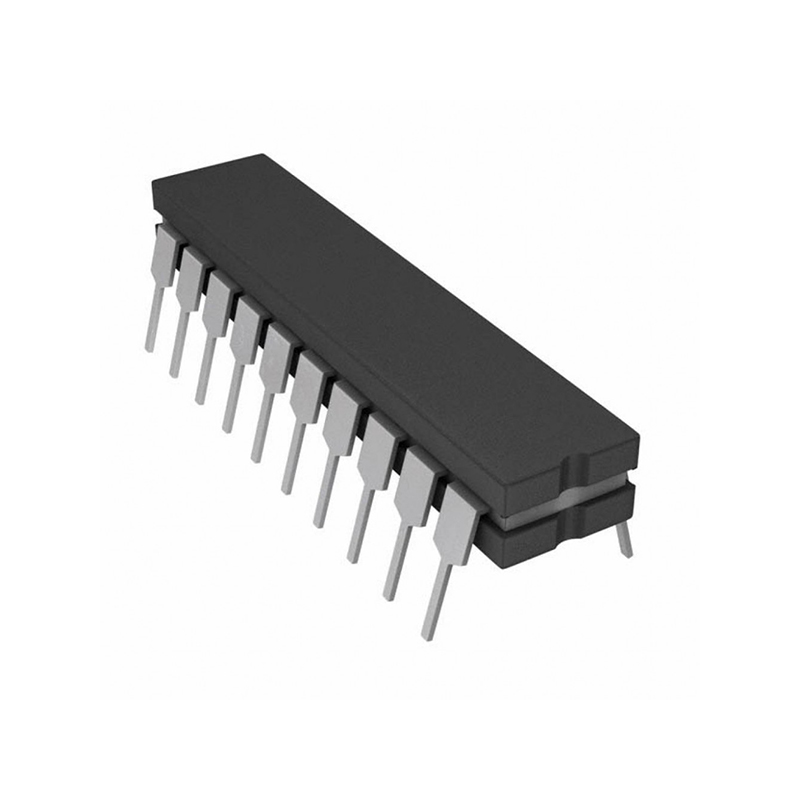

20-Pin PLCC package for easy integration

20-PLCC (9x9)Produttore:

ProduttorePart #:

GAL16V8D-15LJ

Scheda dati:

Pbfree Code:

No

Part Life Cycle Code:

Obsolete

Pin Count:

20

Reach Compliance Code:

not_compliant

EDA/CAD Modelli:

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

The GAL16V8D-15LJ is a versatile and efficient complex programmable logic device (CPLD) designed for medium-scale digital design applications. With its 16 macrocells and a speed grade of 15ns, this CPLD offers high-speed operation and low power consumption, making it an ideal choice for various digital circuit implementations. It belongs to the GAL16V8 family of GAL devices manufactured by Lattice Semiconductor Corporation, known for their advanced CMOS technology

| Pbfree Code | No | Part Life Cycle Code | Obsolete |

| Pin Count | 20 | Reach Compliance Code | not_compliant |

| ECCN Code | EAR99 | HTS Code | 8542.39.00.01 |

| Architecture | PAL-TYPE | Clock Frequency-Max | 45.5 MHz |

| JESD-30 Code | S-PQCC-J20 | JESD-609 Code | e0 |

| Length | 8.9662 mm | Moisture Sensitivity Level | 1 |

| Number of Dedicated Inputs | 8 | Number of I/O Lines | 8 |

| Number of Inputs | 18 | Number of Outputs | 8 |

| Number of Product Terms | 64 | Number of Terminals | 20 |

| Operating Temperature-Max | 70 °C | Operating Temperature-Min | |

| Organization | 8 DEDICATED INPUTS, 8 I/O | Output Function | MACROCELL |

| Peak Reflow Temperature (Cel) | 225 | Power Supplies | 5 V |

| Programmable Logic Type | EE PLD | Propagation Delay | 15 ns |

| Qualification Status | Not Qualified | Seated Height-Max | 4.572 mm |

| Supply Voltage-Max | 5.25 V | Supply Voltage-Min | 4.75 V |

| Supply Voltage-Nom | 5 V | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | COMMERCIAL |

| Terminal Finish | Tin/Lead (Sn85Pb15) | Terminal Form | J BEND |

| Terminal Pitch | 1.27 mm | Terminal Position | QUAD |

| Time@Peak Reflow Temperature-Max (s) | 30 | Width | 8.9662 mm |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | - | - |

I prezzi sottostanti sono solo di riferimento.

Tutte le distinte materiali (BOM) possono essere inviate via e-mail a ![]() [email protected],

oppure compila il modulo sottostante per richiedere un preventivo per GAL16V8D-15LJ, preventivi garantiti entro

[email protected],

oppure compila il modulo sottostante per richiedere un preventivo per GAL16V8D-15LJ, preventivi garantiti entro

![]() 12 ore.

12 ore.

GAL16V8D-25LPN

LATTICE SEMICONDUCTOR CORP

Fast EE PLD with 25ns performance

PALCE20V8H-25PC/4

lattice

PAL-type CMOS integrated circuit

PALCE610H-25PC

lattice

With the PALCE610H-25PC, users can quickly and easily implement custom logic solutions for their projects

5962-8983904RA

lattice

This advanced PLD product, numbered 5962-8983904RA, combines the latest EE technology with a PAL-type architecture

GAL16V8D-10LPN

Lattice Semiconductor Corp

High Performance E2 CMOS PLD Generic Array Logic