Metodo di pagamento

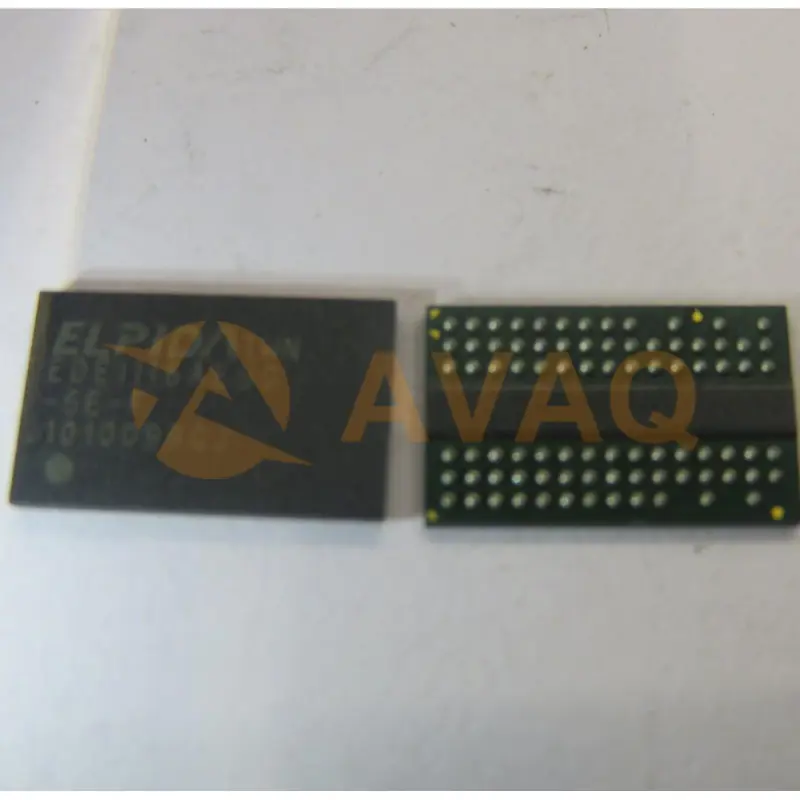

DDR DRAM, 64MX16, 0.45ns, CMOS, PBGA84, HALOGEN FREE AND ROHS COMPLIANT, FBGA-84

BGAProduttore:

ELPIDA

ProduttorePart #:

EDE1116AEBG-6E-F

Scheda dati:

Pacchetto/custodia:

BGA

Tipologia di prodotto:

EDA/CAD Modelli:

Invia tutte le distinte materiali a ![]() [email protected],

oppure compila il modulo sottostante per un preventivo su EDE1116AEBG-6E-F. Risposta garantita entro

[email protected],

oppure compila il modulo sottostante per un preventivo su EDE1116AEBG-6E-F. Risposta garantita entro

![]() 12hr.

12hr.

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

Double-data-rate architecture; two data transfers per clock cycle

The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

DQS is edge-aligned with data for READs; center aligned with data for WRITEs

Differential clock inputs (CK and /CK)

DLL aligns DQ and DQS transitions with CK transitions

Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

Data mask (DM) for write data

Posted /CAS by programmable additive latency for better command and data bus efficiency

Programmable RDQS, /RDQS output for making 8 organization compatible to 4 organization

/DQS, (/RDQS) can be disabled for single-ended Data Strobe operation

Off-Chip Driver (OCD) impedance adjustment is not supported.

| Product Category | Memory ICs |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | - | - |

I prezzi sottostanti sono solo di riferimento.