Metodo di pagamento

MPU integrated host processor

TBGA-352Produttore:

ProduttorePart #:

XPC8240LZU200E

Scheda dati:

Mounting Style:

SMD/SMT

Core:

603e

Number Of Cores:

1 Core

Data Bus Width:

32 bit

EDA/CAD Modelli:

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

PowerPC 603e Microprocessor IC MPC82xx 1 Core, 32-Bit 200MHz 352-TBGA (35x35)

| Product Category | Microprocessors - MPU | Mounting Style | SMD/SMT |

| Core | 603e | Number of Cores | 1 Core |

| Data Bus Width | 32 bit | Maximum Clock Frequency | 200 MHz |

| L1 Cache Instruction Memory | 16 kB | L1 Cache Data Memory | 16 kB |

| Operating Supply Voltage | 2.5 V | Minimum Operating Temperature | 0 C |

| Maximum Operating Temperature | + 105 C | I/O Voltage | 3.3 V |

| Instruction Type | Floating Point | Interface Type | I2C, PCI |

| Memory Type | L1 Cache | Number of Timers/Counters | 4 Timer |

| Processor Series | PowerQUICC II | Product Type | Microprocessors - MPU |

| Subcategory | Microprocessors - MPU | Watchdog Timers | Watchdog Timer |

| Unit Weight | 0.326178 oz | Source Content uid | XPC8240LZU200E |

| Part Life Cycle Code | Obsolete | Reach Compliance Code | |

| ECCN Code | 3A991.A.2 | HTS Code | 8542.31.00.01 |

| Technology | CMOS | uPs/uCs/Peripheral ICs Type | MICROPROCESSOR, RISC |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | - | - |

I prezzi sottostanti sono solo di riferimento.

Tutte le distinte materiali (BOM) possono essere inviate via e-mail a ![]() [email protected],

oppure compila il modulo sottostante per richiedere un preventivo per XPC8240LZU200E, preventivi garantiti entro

[email protected],

oppure compila il modulo sottostante per richiedere un preventivo per XPC8240LZU200E, preventivi garantiti entro

![]() 12 ore.

12 ore.

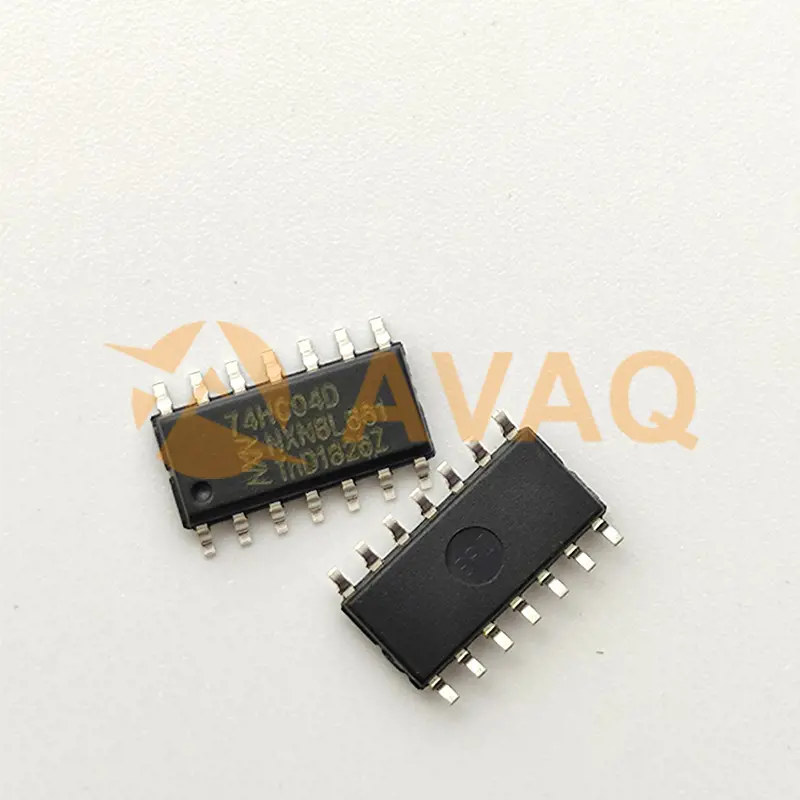

74HC04D

Toshiba

5000+ $0,072

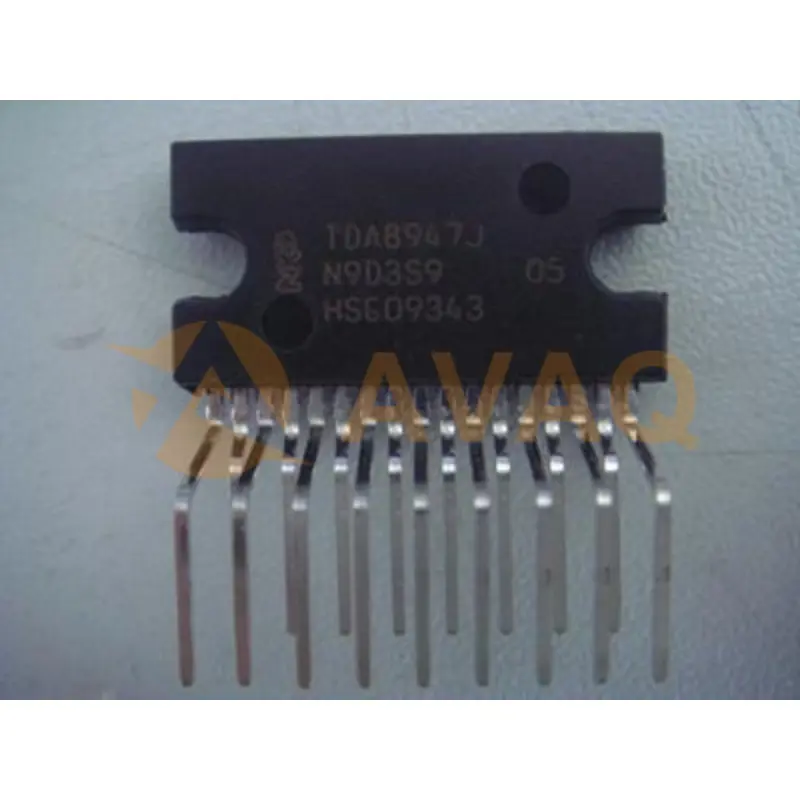

TDA8947J

NXP

Audio Amplifiers 3/4 CHANNEL AUDIO AMPLIFIER

TDA8920BJ

Nxp

Experience crystal-clear sound quality and robust power handling with this efficient Class D amplifier

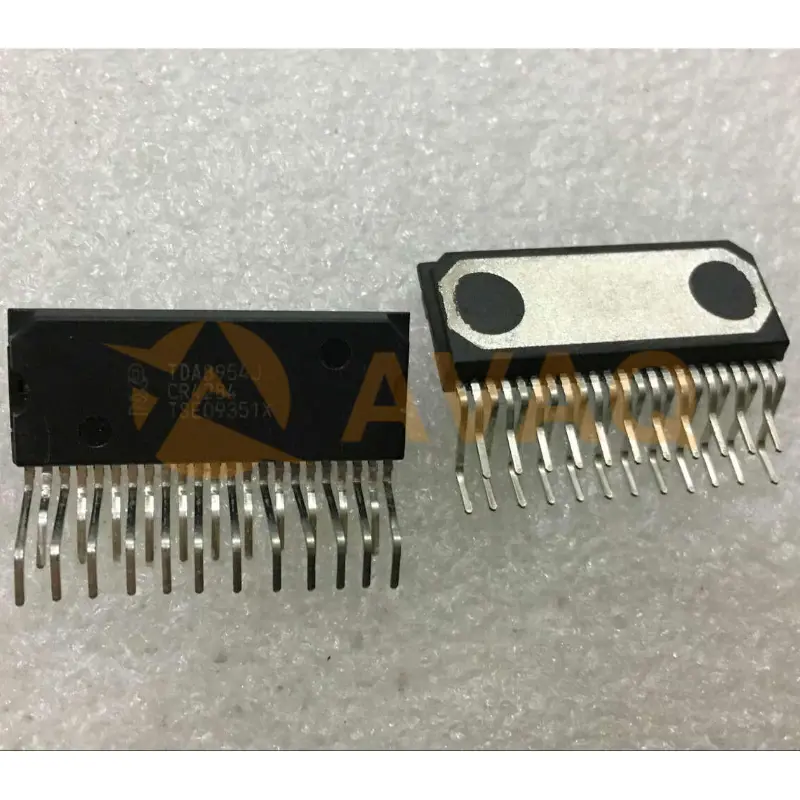

TDA8954J

Nxp

Plastic SOT411-1 PZFM23 audio amplifier

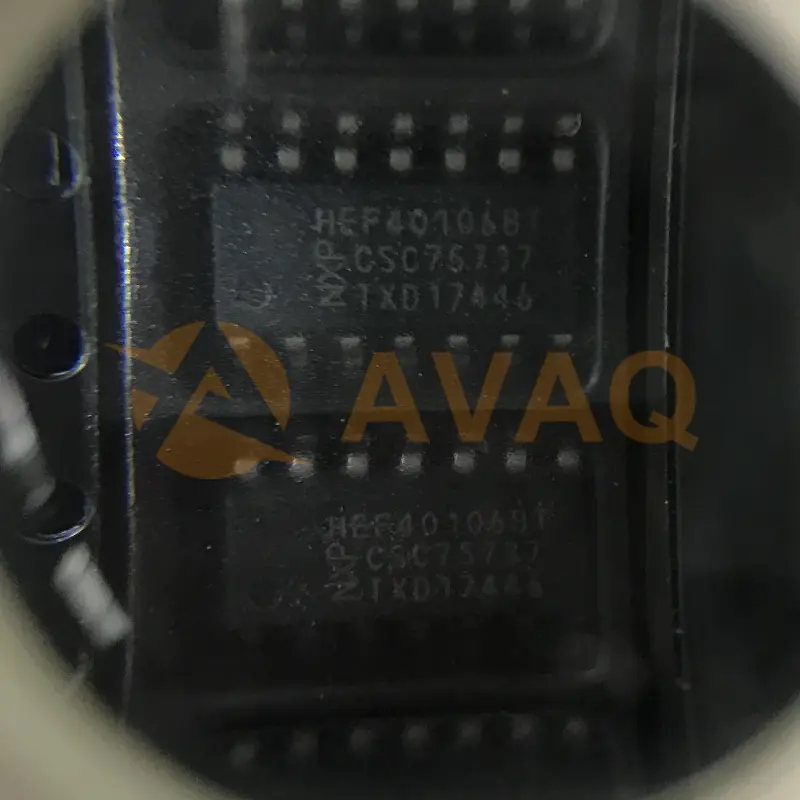

HEF40106BT

Nexperia

Inverter Schmitt Trigger 6-Element CMOS 14-Pin SO