Metodo di pagamento

Low-power, low-latency device for modern embedded systems

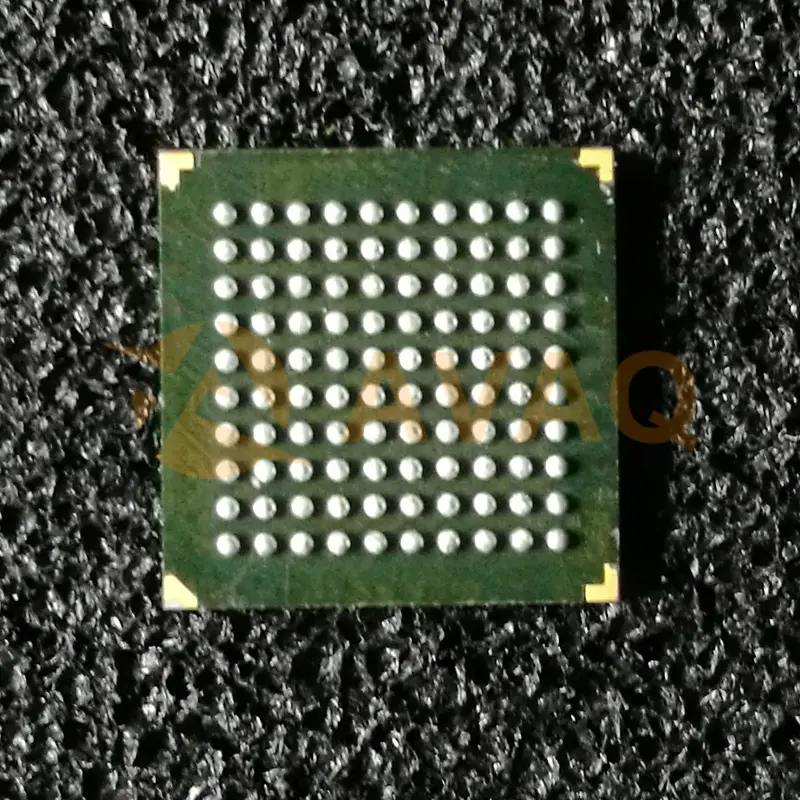

nFBGA-100Produttore:

ProduttorePart #:

SCANSTA112SM

Scheda dati:

Pbfree Code:

Yes

Part Life Cycle Code:

Active

Pin Count:

100

Reach Compliance Code:

not_compliant

EDA/CAD Modelli:

Invia tutte le distinte materiali a ![]() [email protected],

oppure compila il modulo sottostante per un preventivo su SCANSTA112SM. Risposta garantita entro

[email protected],

oppure compila il modulo sottostante per un preventivo su SCANSTA112SM. Risposta garantita entro

![]() 12hr.

12hr.

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

The SCANSTA112 extends the IEEE Std. 1149.1 test bus into a multidrop test bus environment. The advantage of a multidrop approach over a single serial scan chain is improved test throughput and the ability to remove a board from the system and retain test access to the remaining modules. Each SCANSTA112 supports up to 7 local IEEE1149.1 scan chains which can be accessed individually or combined serially.

Addressing is accomplished by loading the instruction register with a value matching that of the Slot inputs. Backplane and inter-board testing can easily be accomplished by parking the local TAP Controllers in one of the stable TAP Controller states via a Park instruction. The 32-bit TCK counter enables built in self test operations to be performed on one port while other scan chains are simultaneously tested.

The STA112 has a unique feature in that the backplane port and the LSP0 port are bidirectional. They can be configured to alternatively act as the master or slave port so an alternate test master can take control of the entire scan chain network from the LSP0 port while the backplane port becomes a slave.

| Source Content uid | SCANSTA112SM | Pbfree Code | Yes |

| Part Life Cycle Code | Active | Pin Count | 100 |

| Reach Compliance Code | not_compliant | ECCN Code | EAR99 |

| HTS Code | 8542.39.00.01 | External Data Bus Width | |

| JESD-30 Code | S-PBGA-B100 | Moisture Sensitivity Level | 3 |

| Number of Terminals | 100 | Peak Reflow Temperature (Cel) | 235 |

| Surface Mount | YES | Technology | CMOS |

| Temperature Grade | INDUSTRIAL | Terminal Finish | Tin/Lead (Sn/Pb) |

| Terminal Form | BALL | Terminal Position | BOTTOM |

| Time@Peak Reflow Temperature-Max (s) | NOT SPECIFIED | uPs/uCs/Peripheral ICs Type | MICROPROCESSOR CIRCUIT |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | $22,844 | $22,84 |

| 30+ | $21,892 | $656,76 |

I prezzi sottostanti sono solo di riferimento.