Metodo di pagamento

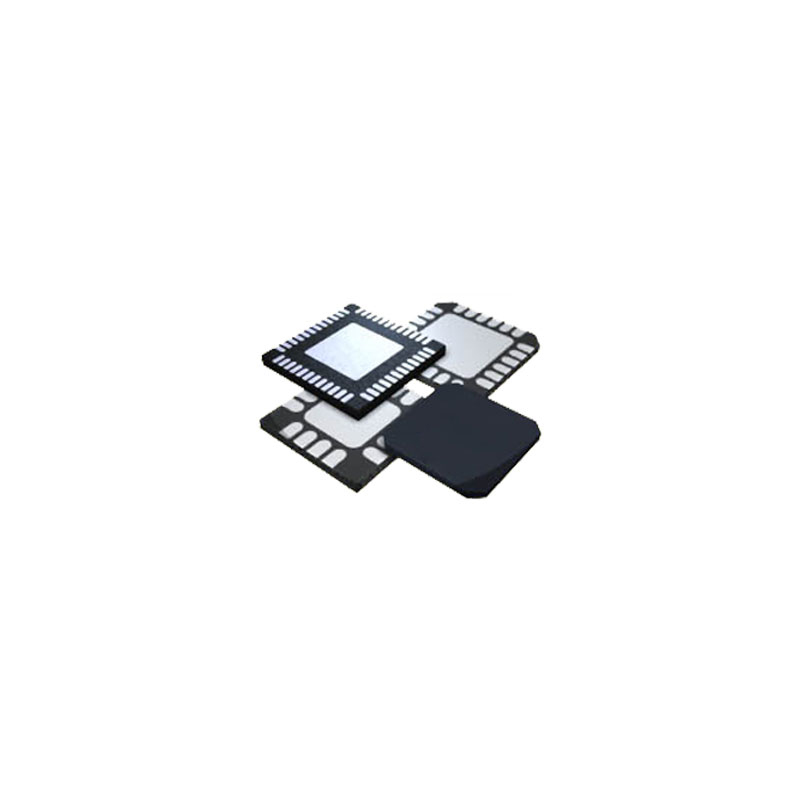

ATM UNI Quad 155.52Mbps 3.3V 304-Pin SBGA

BGAProduttore:

ProduttorePart #:

PM5349-BI

Scheda dati:

Launch_date:

Jul 22, 1999

Last_inspection_date:

+90

Supplier_cage_code:

60991

Htsusa:

8542390001

EDA/CAD Modelli:

Invia tutte le distinte materiali a ![]() [email protected],

oppure compila il modulo sottostante per un preventivo su PM5349-BI. Risposta garantita entro

[email protected],

oppure compila il modulo sottostante per un preventivo su PM5349-BI. Risposta garantita entro

![]() 12hr.

12hr.

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

The PM5349 S/UNI-QUAD SATURN User Network Interface is a monolithic integrated circuit that implements four channel SONET/SDH processing and ATM mapping functions at the STS-3c (STM-1) 155.52 Mbit/s rate.

The S/UNI-QUAD receives SONET/SDH streams using a bit serial interface,recovers the clock and data and processes section, line, and path overhead. It performs framing (A1, A2), de-scrambling, detects alarm conditions, and monitors section, line, and path bit interleaved parity (B1, B2, B3), accumulating error counts at each level for performance monitoring purposes. Line and path far end block error indications (M1, G1) are also accumulated. The S/UNI-QUAD interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope which carries the received ATM cell payload.

The S/UNI-QUAD frames to the ATM payload using cell delineation. HCS error correction is provided. Idle/unassigned cells may be dropped according to a programmable filter. Cells are also dropped upon detection of an uncorrectable header check sequence error. The ATM cell payloads are descrambled. The ATM cells that are passed are written to a four cell FIFO buffer. The received cells are read from the FIFO using a 16-bit wide Utopia level 2 compliant datapath interface. Counts of received ATM cell headers that are errored and uncorrectable and also those that are errored and correctable are accumulated independently for performance monitoring purposes.

The S/UNI-QUAD transmits SONET/SDH streams using a bit serial interface and formats section, line, and path overhead appropriately. It synthesizes the transmit clock from a lower frequency reference and performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section, line, and path bit interleaved parity (B1, B2, B3) as required to allow performance monitoring at the far end. Line and path far end block error indications (M1, G1) are also inserted. The S/UNI-QUAD generates the payload pointer (H1, H2) and inserts the synchronous payload envelope which carries the ATM cell payload.The S/UNI-QUAD also supports the insertion of a large variety of errors into the transmit stream, such as framing pattern errors, bit interleaved parity errors, and illegal pointers, which are useful for system diagnostics and tester applications.

ATM cells are written to an internal four cell FIFO using a 16-bit wide Utopia Level 2 datapath interface. Idle/unassigned cells are automatically inserted when the internal FIFO contains less than one cell. The S/UNI-QUAD provides generation of the header check sequence and scrambles the payload of the ATMcells. Each of these transmit ATM cell processing functions can be enabled or bypassed.

No line rate clocks are required directly by the S/UNI-QUAD as it synthesizes the transmit clock and recovers the receive clock using a 19.44 MHz reference clock.The S/UNI-QUAD outputs a differential TTL (externally coverted to PECL) line data (TXD+/-).

The S/UNI-QUAD is configured, controlled and monitored via a generic 8-bit microprocessor bus interface. The S/UNI-QUAD also provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

The S/UNI-QUAD is implemented in low power, +3.3 Volt, CMOS technology. It has TTL and pseudo-ECL (PECL) compatible inputs and TTL/CMOS compatible outputs and is packaged in a 304 pin SBGA package.

| place | launch_date | Jul 22, 1999 | |

| last_inspection_date | +90 | supplier_cage_code | 60991 |

| htsusa | 8542390001 | schedule_b | 8542390000 |

| ppap | aec | ||

| RadHard | No | Dose Level | N/A |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | - | - |

I prezzi sottostanti sono solo di riferimento.

RTC6705

Microchip

5.8GHz FM Transmitter

VSC8531XMW-05

MICROCHIP

Gigabit Ethernet Transceiver with RMII/RGMII & 1588 SoF Support.1 Port GbE Cu PHY with RGMII/RMII (Ind. Temp).

VSC8541XMV

Microchip

VSC8541XMV product description

VSC8531XMW-02

MICROCHIP

Gigabit Ethernet Transceiver with RMII/RGMII & 1588 SoF Support.1 Port GbE Cu PHY with RGMII/RMII (Ind. Temp).

VSC7512XMY

Microchip Technology, Inc

Telecom IC Ethernet Switch 172-QFN