Metodo di pagamento

EE PLD, 10ns, 192-Cell, CMOS, PQFP144, LEAD FREE, TQFP-144

TQFP-144Produttore:

Lattice Semiconductor Corporation

ProduttorePart #:

M4A5-192/96-10VNC

Scheda dati:

Pbfree Code:

Yes

Part Life Cycle Code:

Active

Pin Count:

144

Reach Compliance Code:

compliant

EDA/CAD Modelli:

Invia tutte le distinte materiali a ![]() [email protected],

oppure compila il modulo sottostante per un preventivo su M4A5-192/96-10VNC. Risposta garantita entro

[email protected],

oppure compila il modulo sottostante per un preventivo su M4A5-192/96-10VNC. Risposta garantita entro

![]() 12hr.

12hr.

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

GENERAL DESCRIPTIONThe ispMACH™ 4A family from Lattice offers an exceptionally flexible architecture and delivers a superior Complex Programmable Logic Device (CPLD) solution of easy-to-use silicon products and software tools. The overall benefits for users are a guaranteed and predictable CPLD solution, faster time-to-market, greater flexibility and lower cost. The ispMACH 4A devices offer densities ranging from 32 to 512 macrocells with 100% utilization and 100% pin-out retention. The ispMACH 4A families offer 5-V (M4A5- xxx) and 3.3-V (M4A3-xxx) operation.

| Pbfree Code | Yes | Part Life Cycle Code | Active |

| Pin Count | 144 | Reach Compliance Code | compliant |

| ECCN Code | EAR99 | HTS Code | 8542.39.00.01 |

| Additional Feature | YES | Clock Frequency-Max | 62.5 MHz |

| In-System Programmable | YES | JESD-30 Code | S-PQFP-G144 |

| JESD-609 Code | e3 | JTAG BST | YES |

| Length | 20 mm | Moisture Sensitivity Level | 3 |

| Number of Dedicated Inputs | 16 | Number of I/O Lines | 96 |

| Number of Macro Cells | 192 | Number of Terminals | 144 |

| Operating Temperature-Max | 70 °C | Operating Temperature-Min | |

| Organization | 16 DEDICATED INPUTS, 96 I/O | Output Function | MACROCELL |

| Peak Reflow Temperature (Cel) | 260 | Programmable Logic Type | EE PLD |

| Propagation Delay | 10 ns | Qualification Status | Not Qualified |

| Seated Height-Max | 1.6 mm | Supply Voltage-Max | 5.25 V |

| Supply Voltage-Min | 4.75 V | Supply Voltage-Nom | 5 V |

| Surface Mount | YES | Technology | CMOS |

| Temperature Grade | COMMERCIAL | Terminal Finish | MATTE TIN |

| Terminal Form | GULL WING | Terminal Pitch | 0.5 mm |

| Terminal Position | QUAD | Time@Peak Reflow Temperature-Max (s) | 40 |

| Width | 20 mm |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | - | - |

I prezzi sottostanti sono solo di riferimento.

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

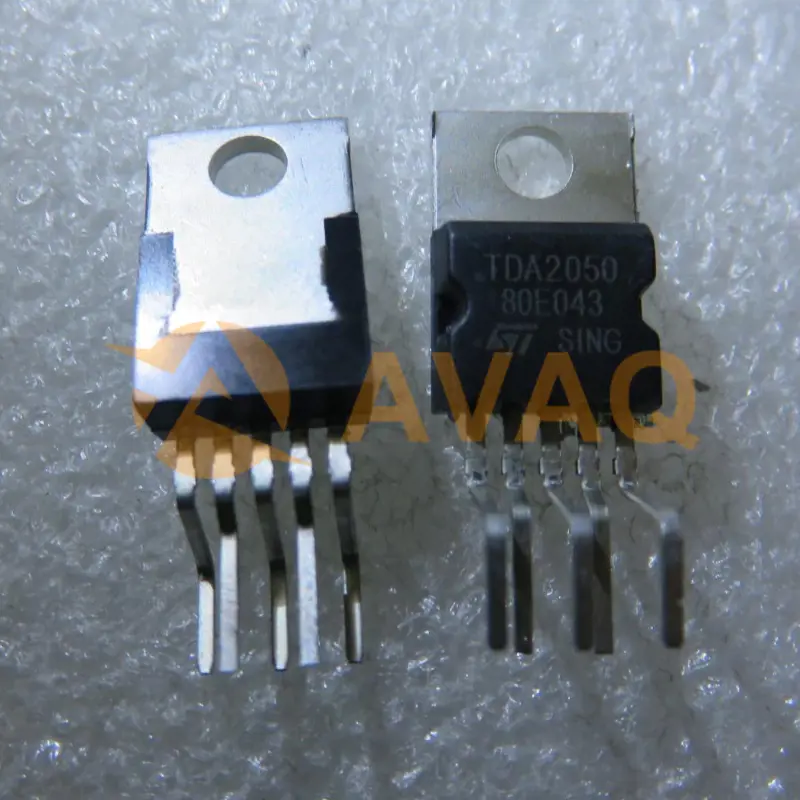

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power

DS1307+

Analog Devices

I2C DIP-8 Real-time Clocks (RTC) ROHS