Metodo di pagamento

Video Clock Generator

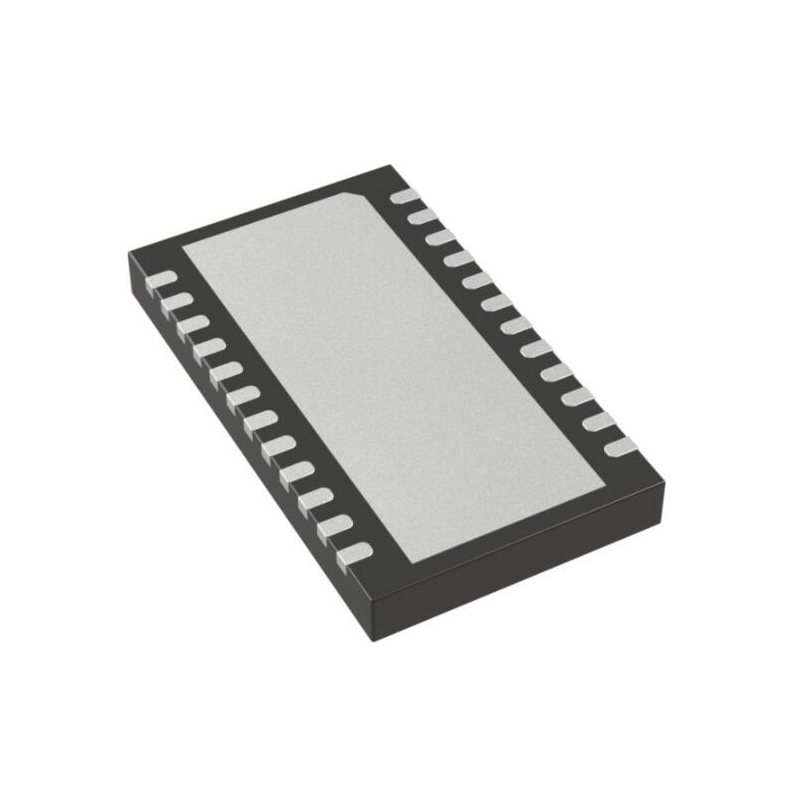

WQFN EPProduttore:

Texas Instruments

ProduttorePart #:

LMH1983SQE

Scheda dati:

ECCN (US):

EAR99

Automotive:

No

PPAP:

No

Typical Duty Cycle (%):

50

EDA/CAD Modelli:

Invia tutte le distinte materiali a ![]() [email protected],

oppure compila il modulo sottostante per un preventivo su LMH1983SQE. Risposta garantita entro

[email protected],

oppure compila il modulo sottostante per un preventivo su LMH1983SQE. Risposta garantita entro

![]() 12hr.

12hr.

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

Description for the LMH1983The LMH1983 is a highly-integrated programmable audio/video (A/V) clock generator intended for broadcast and professional applications. It can replace multiple PLLs and VCXOs used in applications supporting SMPTE serial digital video (SDI) and digital audio AES3/EBU standards. It offers low-jitter reference clocks for any SDI transmitter to meet stringent output jitter specifications without additional clock cleaning circuits.The LMH1983 features automatic input format detection, simple programming of multiple A/V output formats, genlock or digital free-run modes, and override programmability of various automatic functions. The recognized input formats include HVF syncs for the major video standards, 27 MHz, 10 MHz, and 32/44.1/48/96 kHz audio word clocks.The dual-stage PLL architecture integrates four PLLs with three on-chip VCOs. The first stage (PLL1) uses an external low-noise 27 MHz VCXO with narrow loop bandwidth to provide a clean reference clock for the next stage. The second stage (PLL2, 3, 4) consists of three parallel VCO PLLs for simultaneous generation of the major digital A/V clock fundamental rates, including 148.5 MHz, 148.5/1.001 MHz, and 98.304 MHz (4 × 24.576 MHz). Each PLL can generate a clock and a timing pulse to indicate top of frame (TOF).When locked to reference, an internal 10-bit ADC will track the loop filter control voltage. When a loss of reference (LOR) occurs, the LMH1983 can be programmed to hold the control voltage to maintain output accuracy within ±0.5 ppm (typical) of the previous reference. The LMH1983 can be configured to re-synchronize to a previous reference with glitch-less operation.

| ECCN (US) | EAR99 | Part Status | Obsolete |

| Automotive | No | PPAP | No |

| Typical Duty Cycle (%) | 50 | Maximum Operating Supply Voltage (V) | 3.6 |

| Minimum Operating Temperature (°C) | -40 | Maximum Operating Temperature (°C) | 85 |

| Packaging | Tape and Reel | Mounting | Surface Mount |

| PCB changed | 40 | Pin Count | 40 |

| Lead Shape | No Lead |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | - | - |

I prezzi sottostanti sono solo di riferimento.

AK1573

Asahi Kasei Microdevices/AKM

1000+ $2,489

MN3102

Panasonic

Durable Plastic Package for Moisture-Sensitive Environments

SI5351A-B-GT

Skyworks

Clock Generator Si5351A-B-GT PK

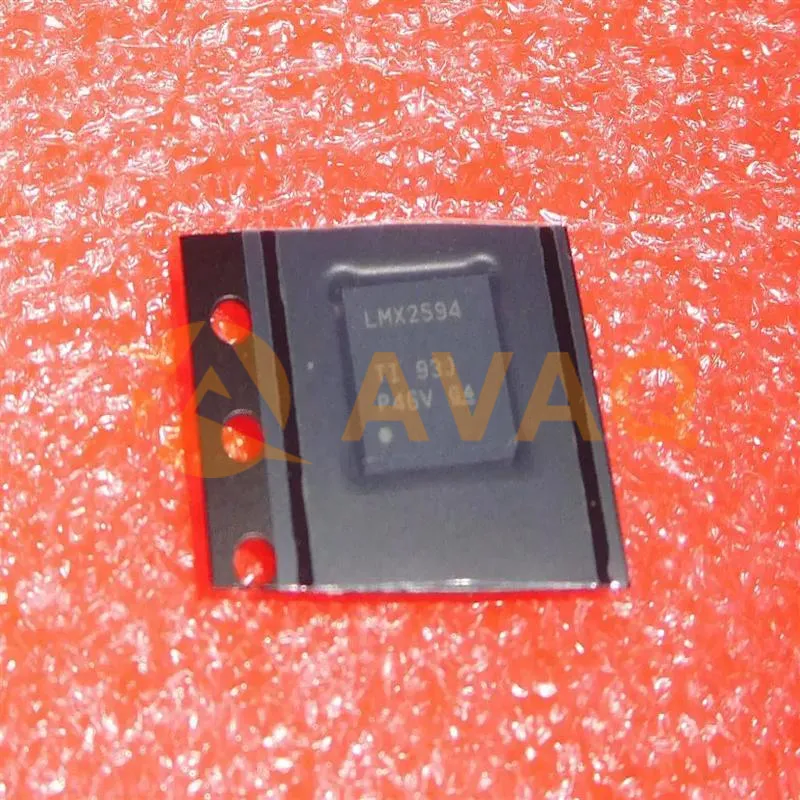

LMX2594RHAT

Texas Instruments

15-GHz wideband PLLatinum™ RF synthesizer with phase synchronization and JESD204B support 40-VQFN -40 to 85"

LM565CN

Texas Instruments

PLL Single 0.25MHz to 0.5MHz 14-Pin MDIP Rail