Metodo di pagamento

Field Programmable Gate Array for customizable applications

FTBGA-256Produttore:

Lattice Semiconductor Corporation

ProduttorePart #:

LCMXO1200C-3FTN256C

Scheda dati:

Pbfree Code:

Yes

Part Life Cycle Code:

Active

Pin Count:

256

Reach Compliance Code:

compliant

EDA/CAD Modelli:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for LCMXO1200C-3FTN256C, guaranteed quotes back within

[email protected],

or fill below form to Quote for LCMXO1200C-3FTN256C, guaranteed quotes back within

![]() 12hr.

12hr.

Compila il breve modulo sottostante e ti forniremo immediatamente il preventivo.

Lattice Semiconductor's LCMXO1200C-3FTN256C FPGA is the perfect choice for cost-sensitive applications that demand high performance and low power consumption. With 1200 LUTs, 64 Kbit Embedded Block RAM, and 18 I/O pins, this FPGA offers the flexibility and connectivity needed for industrial control systems, consumer electronics, automotive infotainment, and communication equipment. Its compact 256-pin TQFP package makes it suitable for space-constrained designs, while its maximum frequency of 75 MHz ensures efficient operation. Plus, with a supply voltage of 1.2V, this FPGA is designed for low power consumption, making it an excellent choice for a wide range of applications

| Pbfree Code | Yes | Part Life Cycle Code | Active |

| Pin Count | 256 | Reach Compliance Code | compliant |

| ECCN Code | 3A991.D | HTS Code | 8542.39.00.01 |

| JESD-30 Code | S-PBGA-B256 | JESD-609 Code | e1 |

| Length | 17 mm | Moisture Sensitivity Level | 3 |

| Number of CLBs | 150 | Number of Inputs | 211 |

| Number of Logic Cells | 1200 | Number of Outputs | 211 |

| Number of Terminals | 256 | Operating Temperature-Max | 85 °C |

| Operating Temperature-Min | Organization | 150 CLBS | |

| Peak Reflow Temperature (Cel) | 260 | Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY |

| Qualification Status | Not Qualified | Seated Height-Max | 1.7 mm |

| Supply Voltage-Max | 3.465 V | Supply Voltage-Min | 1.71 V |

| Supply Voltage-Nom | 1.8 V | Surface Mount | YES |

| Temperature Grade | OTHER | Terminal Finish | Tin/Silver/Copper (Sn96.5Ag3.0Cu0.5) |

| Terminal Form | BALL | Terminal Pitch | 1 mm |

| Terminal Position | BOTTOM | Time@Peak Reflow Temperature-Max (s) | 40 |

| Width | 17 mm |

Relativi al servizio post-vendita e alla liquidazione

Pagamento

Pagamento

Metodo di pagamento

Per canali di pagamento alternativi, contattaci a:

[email protected] Spedizione e imballaggio

Spedizione e imballaggio

metodo di spedizione

AVAQ determina e confeziona tutti i dispositivi in base ai requisiti di protezione contro le scariche elettrostatiche (ESD) e il livello di sensibilità all'umidità (MSL)..

Garanzia

Garanzia

Prodotto 365 giorni

Qualità garantita

Promettiamo di fornire un servizio di garanzia della qualità di 365 giorni per tutti i nostri prodotti.

| Qtà. | Prezzo unitario | Est. Prezzo |

|---|---|---|

| 1+ | $23,857 | $23,86 |

| 200+ | $9,233 | $1.846,60 |

| 500+ | $8,908 | $4.454,00 |

| 1000+ | $8,747 | $8.747,00 |

I prezzi sottostanti sono solo di riferimento.

C100

Issi

Video ICs 4MP H.265 Video Processor - 64MB DDR2, BGA85, 5mm x 6mm

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

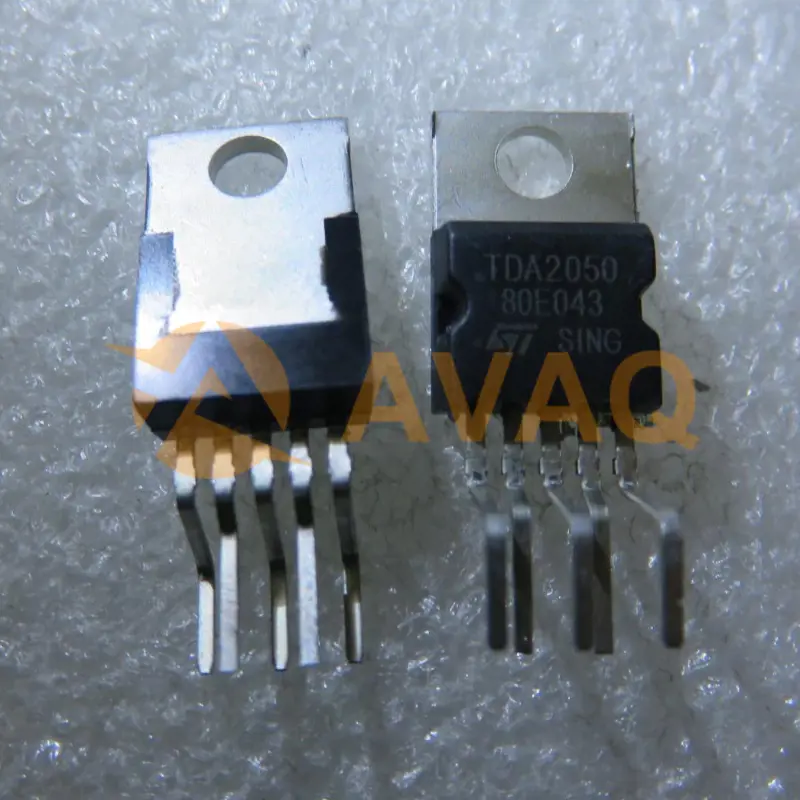

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power